-

SPICE模型

SPICE模型基带建模

• BSIMProPlus

射频建模

• MeQLab

自动化提取

• SDEP

验证评估

• ME-Pro

-

PDK

PDKPCell开发

• PCellLab

PDK验证

• PQLab

-

标准单元库

标准单元库特征化

• NanoCell

验证

• LibWiz

-

制造

制造光刻工艺建模仿真

• FabLitho

掩模版自动化设计

• FAR

-

电路设计平台

电路设计平台原理图设计

• NanoDesigner SE

版图编辑

• NanoDesigner LS

交互式物理验证

• NanoDesigner iV

设计优化

• NanoDesigner Optimizer

-

电路仿真

电路仿真SPICE仿真器

• NanoSpice • NanoSpice X • NanoSpice Giga

FastSPICE仿真器

• NanoSpice Pro • NanoSpice Pro X

混合信号仿真

• NanoSpice MS

波形查看分析

• NanoWave

-

电路分析

电路分析动态和静态电路检查

• NanoSpice CCK

良率分析

• NanoYield

信号完整性分析

• NanoSpice SI

路径分析

• PathInspector

功率及电源芯片设计验证

• PTM

电源网络分布分析

• RNi

ESD验证

• ESDi

-

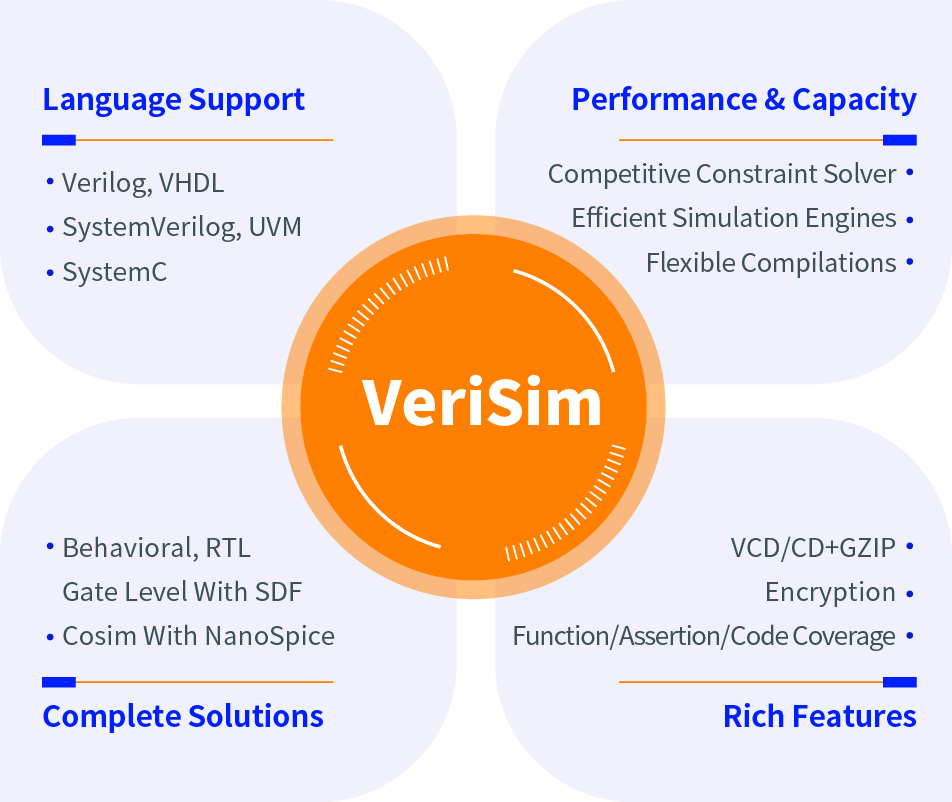

电路仿真

电路仿真数字仿真

• VeriSim

-

标准单元库

标准单元库特征化

• NanoCell

验证

• LibWiz

-

SoC设计与验证

SoC设计与验证时序分析

• TRASTA

设计布局规划

• NavisPro

信号完整性

• NanoSpice SI

电源分析

• PTM

ESD验证

• ESDi

芯片封装连接验证

• PadInspector